# Comparison of interpolator realizations for high quality audio signals

Adam Dąbrowski<sup>+</sup>, Krzysztof Sozański<sup>#</sup>

<sup>+</sup>Poznań University of Technology, Institute of Electronics and Telecommunications Division for Electronic Systems and Signal Processing, ul. Piotrowo 3a, 60-965 Poznań, Poland, Tel. + 48 61 8 782 745, Fax. + 48 61 8 782 572, e-mail: dabrow@et.put.poznan.pl currently at University of Kaiserslautern, Dept. of Electrical Eng., Paul-Ehrlich-Str. 14/445, 67-663 Kaiserslautern, Germany, Phone: (+ 49 631) 2052839, Fax: (+ 49 631) 2052168 <sup>#</sup> Department of Mathematics, Physics and Technology, Pedagogical University of Zielona Góra, al. Wojska Polskiego 69, 65-625 Zielona Góra, Poland, Tel. + 48 68 263520 int. 241, Fax. + 48 68 265449, e-mail: sozanski@asia.aw.wsp.zgora.pl, sozanski@ieee.org.

## ABSTRACT

This paper describes implementations of a single stage and a multistage interpolator for high quality audio signals. The first one is a multistage interpolator based on bireciprocal modified lattice wave digital filters. The second one is that based on two-path (polyphase) digital filters. The interpolators are implemented in a floating point digital signal processor ADSP-21061 (SHARC). The results of these implementations are presented and compared.

**Keywords**: digital signal interpolators, multirate signal processing, modified wave digital filters, IIR digital filters, digital signal processors.

#### **1. INTRODUCTION**

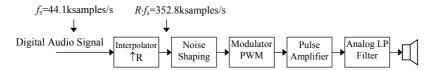

In a class D power amplifier, depicted in Fig. 1, the output pulse power amplifier works as a one-bit D/A converter. We assume that the amplifier input signal is in the CD player standard, i.e., is sampled with rate  $f_s$ =44.1 ksamples/s. Thus, its approximate frequency band covers 0.. $f_b$ =0...20 kHz. In order to increase the resolution of the amplifier, noise shaping and oversampling techniques are used.

Fig. 1. Block diagram of digital audio power amplifier

The chosen signal oversampling ratio R=8 is a compromise between the power MOSFET switching losses (for the minimization of which R should be also minimized) and the

selectivity of the output passive lowpasss smoothing filter. The chosen switching frequency is  $Rf_s=352.8$ kHz. During the signal interpolation process, the signal dynamic ratio can be decreased by adding mirror signals to the input signal. For high quality audio signals the required dynamic range is near 90dB.

#### 2. INTERPOLATOR DESIGN PARAMETERS

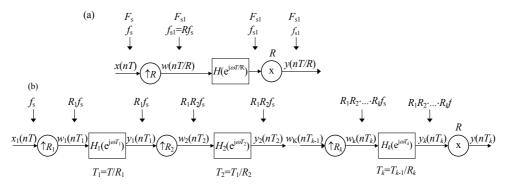

An interpolator made up of an upsampler and an anti-imaging filter is depicted in Fig. 2a. After the upsampling process, the out-of-band signal is a potential source of interference for the input signal. The out of band signal can decrease the signal dynamic ratio. The anti-imaging filter must attenuate all interfering signals. The stopband cutoff frequency  $F_z$  must be selected to limit aliasing in the input signal frequency range.

Fig. 2. Interpolator made up of upsampler and an anti-imaging filter: (a) single stage version, (b) multistage version

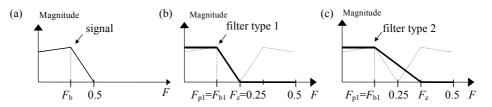

Two types of stopband criteria can be used in practice. In type 1, aliasing above the stopband deviation level in the transition band is not allowed (Fig. 3b). In type 2, aliasing above the stopband deviation level in the transition band is allowed (Fig. 3c). The normalized stopband frequency  $F_z$  for filters of type 1 and type 2 can be described by equations

$$F_{z} = \frac{F_{s}}{2R}$$

,  $F_{z} = \frac{F_{s}}{R} - \frac{F_{b}}{R}$ , (1a,b)

respectively, where:  $F_b$  – the normalized passband frequency of the input signal, and  $F_s$  – the normalized sampling rate, R – oversampling ratio.

The multistage version of the interpolator is depicted in Fig. 2b. In this case, a design strategy is used, in which every stage attenuates its own interfering signals. Normalized passband signal frequency on the output of every stage is given by

$$F_{bk} = \frac{F_{b(k-1)}}{R_k} \quad , (2)$$

where:  $R_k$  – interpolating ratio at stage k. For stage k of the interpolator with a filter type 1 and type 2, the stopband frequency is given by

$$F_{zk} = \frac{F_{s(k-1)}}{2R_k} \quad , \quad F_{zk} = \frac{F_{s(k-1)}}{R_k} - \frac{F_{b(k-1)}}{R_k} \quad . \tag{3a,b}$$

respectively.

For the high quality audio signal with a dynamic range near to 90 dB, a chosen oversampling ratio R=8 and the filter type 2, the parameters for a single stage interpolator and a multistage interpolator are shown in Table 1. In the multistage interpolator it is possible to reduce requirements for stages 2 and 3 by means of the suppression introduced in the stopband by an analog lowpass filter.

Fig. 3. Filter types: (a) input signal band width, (b) type 1 anti-imaging filter requirements with aliasing not allowed in transition band (for *R*=2), (c) type 2 anti-imaging filter requirements with aliasing allowed in transition band (for *R*=2)

| Stage        | $F_{p}$    | $F_{z}$    | $\delta_{\rm p}  [{ m dB}]$ | $\delta_{\rm z}  [{\rm dB}]$ | $\delta_{ m zFA} [ m dB]$  |

|--------------|------------|------------|-----------------------------|------------------------------|----------------------------|

|              | (passband) | (stopband) | (passband<br>ripple)        | (stopband<br>ripple)         | (with analog<br>LP filter) |

| single stage | 0.0567     | 0.0683     | 0.1                         | -90                          | -90                        |

| 1            | 0.2267     | 0.2732     | 0.033                       | -90                          | -90                        |

| 2            | 0.1134     | 0.3866     | 0.033                       | -90                          | -60                        |

| 3            | 0.0567     | 0.4433     | 0.033                       | -90                          | -60                        |

Table 1. Design parameters for single stage interpolator and multistage interpolator

#### **3. SINGLE STAGE INTERPOLATOR**

The authors designed and implemented a single-stage interpolator with parameters shown in Table 1 in a digital signal processor ADSP-21061 [1]. The following types of interpolators have been analyzed:

- an interpolator with an elliptic filter IIR (Elip),

- interpolators with polyphase FIR filters: Parks-McClellan (PM), Kaiser window (Kaiser), least squares (LS), and constrained least squares (CLS).

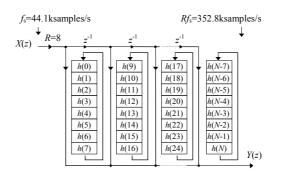

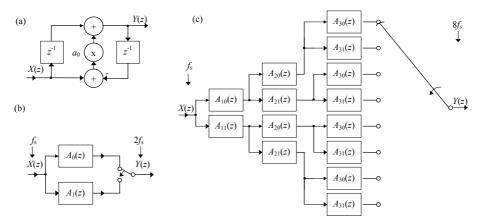

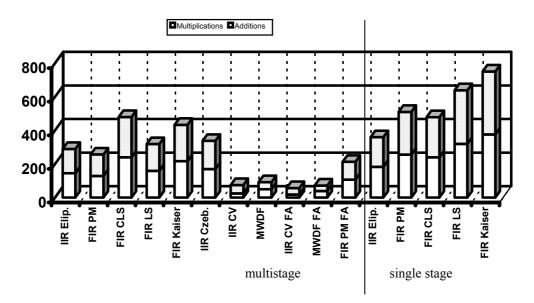

Fig. 7 shows the quantity of arithmetical operations necessary for a one sample interpolation (where R=8). Interpolators with FIR filters have a polyphase structure with periodically time-varying coefficients (Fig. 4). From the filters analyzed the IIR filters required the least number of arithmetical operations, however the polyphase FIR filters showed a similar efficiency.

Fig. 4. Polyphase interpolator with periodically time-varying coefficients for R=8

## 4. MULTISTAGE INTERPOLATOR

The multistage interpolator with parameters in Table 1 was designed and realized using a digital signal processor ADSP-21061. The following types of interpolators have been analyzed:

- interpolators with FIR filters (Section 3) and the FIR Parks-McClellan filter (PM FA) employing a stopband characteristic of an analog lowpass filter(Fig. 1),

- classical IIR filters, elliptic (Elip.) and Czebyshev (Czeb.).

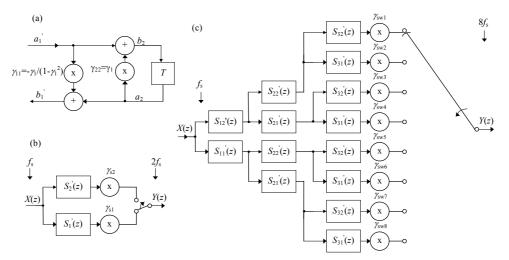

Fig. 5. Interpolator realized with modified wave digital filters: (a) modified allpass wave digital filter, (b) interpolator with R=2, (c) multistage version of the interpolator for R=8 with a single switch and resultant multipliers

Bireciprocal lattice modified wave digital filters were also used in the interpolator design [1, 2, 4]. A block diagram of the filters is depicted in Fig. 5b,c. Two versions of this

interpolator were realized (MWDF and MWDF FA). The characteristics of an analog lowpass filter (Fig. 1) were employed in the second version. Modified wave digital filters are very efficient for the implementation with modern floating point signal processors, especially for applications where a wide dynamic range of the signal is important.

Among the polyphase IIR filters, special attention was paid to a two-path (polyphase) filter designed according to methods introduced by Venezuela and Constantindes [5]. This filter consists of two branches with allpass filters (Fig. 6a). A block diagrams of these filters are shown in Figs. 6b,c. The two-path filters have very high performance and they are easily implemented and computationally efficient. The quantity N of allpass filter stages depends on: the stopband ripple  $\delta_z$  and the relative frequency of transition bandwidth  $\Delta F$  and is given by [3]

$$N = \delta_z / (72\Delta F + 10) \quad . \tag{4}$$

Similar to that for wave digital filters, two implementations of the polyphase two-path filters (CV and CV FA) were realized (Fig. 7).

Fig. 6. Block diagram of interpolator realized by polyphase two-path filters: (a) allpass section, (b) interpolator for R=2, (c) multistage version of the interpolator for R=8 with a single switch

### 5. CONCLUSION

Among the analyzed filters (Fig. 7) the multistage interpolator based on a polyphase twopath filter required the smallest number of arithmetical operations for implementation with ADSP-21061 digital signal processor. For applications, for which a linear phase response is important, a multistage interpolator with a Parks-McClellan FIR filter requires the smallest number of arithmetical operations. Using the symmetry of FIR filter coefficients, it is possible to decrease the number of arithmetic operations. Good results are also obtained for multistage interpolators based on modified wave digital filters.

Fig. 7. Quantity of arithmetical operations for interpolation of one sample (for *R*=8), results of implementations of single stage and multistage versions of the interpolator realized on ADSP-21061 digital signal processor

## REFERENCES

- Dąbrowski A., Sozański K., Implementation of Multirate Modified Wave Digital Filters Using Digital Signal Processors, XXI Krajowa Konferencja Teoria Obwodów i Układy Elektroniczne, KKTUIE98, Poznań 1998.

- [2] Fettweis A. Modified Wave Digital Filters for Improved Implementation by Commercial Digital Signal Processors, Signal Processing 16, Elsever Science Publishers B.V. (North-Holland), 1989.

- [3] Krukowski A., Kale I., Morling R. C. S., Hejn K., A Design Technique for Polyphase Decimators with Binary Constrained Coefficients for High Resolution A/D Converters, IEEE International Symposium on Circuits and Systems (ISCAS'94), Vol. 2, 1994, pp. 533-536.

- [4] Sozański K., Projektowanie i badanie banków filtrów cyfrowych realizowanych za pomocą procesorów sygnałowych, Rozprawa Doktorska, Politechnika Poznańska, Wydział Elektryczny, Poznań 1999.

- [5] Venezuela R. A., Constantindes A. G., Digital Signal Processing Schemes for Eefficient Interpolation and Decimation, IEE Proceedings, Vol. 130, Part G, No. 6, December 1983, pp. 225-235.